특징

| 애플리케이션

|

특징

| 애플리케이션

|

절대 최대 평점(1)

달리 명시되지 않는 한, Tamb= 25℃

| 매개변수 | 기호 | 가치 | 단위 |

| 공급 전압 | VDD1/VDD2 | -0.5~6 | V |

| A/B 입력 전압 | VINA/VINB | -0.5 VDD1/VDD2+0.5(2) | V |

| 작동 온도 | Tamb | -40~125 | ℃ |

| 접합 온도 | TJ | 150 | ℃ |

| 보관 온도 | Tstg | -65~150 | ℃ |

| 핀 온도(리플로우 납땜) | 260 | ℃ | |

| 스탠드 전압 정격 절연 | 5 | KVrms(3) |

참고: (1) 작동 조건이 위의 "절대 최대 정격"을 초과하는 경우 기기에 영구적인 손상을 일으킬 수 있습니다. 위의 값은 작동 조건에 대한 최대값일 뿐이며, 이 사양을 벗어나서 기기를 작동하는 것은 권장하지 않습니다. 절대 한계 파라미터 조건에서 장시간 사용 시 기기의 안정성에 영향을 미칠 수 있습니다.

DC 전기적 특성

달리 명시되지 않는 한,VDD=2.5V±5% 또는 3.3V±10% 또는 5V±10%,Tamb= 25℃

| 매개변수 | 기호 | 테스트 조건 | Min | Typ | 최대 | 단위 |

| VDD 저전압 임계값 | VDDUV+ | VDD1, VDD2 상승 | 1.9 | 2.2 | 2.37 | V |

| VDD 저전압 임계값 | VDDUV- | VDD1, VDD2 실패 | 1.85 | 2.12 | 2.32 | V |

| VDD 저전압 히스테리시스 | VDDHYS | 50 | 70 | 95 | mV | |

| 양수 입력 임계값 | VT+ | 모든 입력이 위로 올라갑니다. | 1.4 | 1.6 | 1.9 | V |

| 역방향 입력 임계값 | VT- | 모든 입력 실패 | 1.0 | 1.3 | 1.4 | V |

| 입력 임계값 히스테리시스 | VHYS | 0.38 | 0.44 | 0.50 | V | |

| 높은 레벨 입력 전압 | VIH | 2.0 | - | - | V | |

| 낮은 레벨 입력 전압 | VIL | - | - | 0.8 | V | |

| 높은 레벨 출력 전압 | VOH | loh=-4mA | VDD-0.4 | VDD-0.2 | - | V |

| 낮은 레벨 출력 전압 | VOL | lol=4mA | - | 0.2 | 0.4 | V |

| 입력 누설 전류 | IL | - | - | ±10 | µA | |

| 출력 임피던스(1) | ZO | - | 50 | - | Ω | |

| 입력 전류 활성화 | IENH,IENL | VEN=VIH 또는 VIL | - | 2.0 | - | µA |

| 데이터 요금 | 0 | - | 150 | Mbps | ||

| 최소 펄스 폭 | - | - | 5.0 | ns | ||

| 전파 지연 | tPHL,tPLH | 그림 2 참조 | 5.0 | 9.0 | 15 | ns |

| 펄스 폭 왜곡 |tPLH-tPHL| | PWD | 그림 2 참조 | - | 0.2 | 4.5 | ns |

| 부품 간 지연 스큐(2) | tPSK(P-P) | - | 2.0 | 4.5 | ns | |

| 채널 간 지연 스큐 | tPSK | - | 0.4 | 2.5 | ns | |

| 상승 시간 | tr | CL=15pF, 그림 2 참조 | - | 2.2 | 4.0 | ns |

| 떨어지는 시간 | tf | CL=15pF, 그림 2 참조 | - | 2.2 | 4.0 | ns |

| 피크 아이 다이어그램 지터 | tJIT(PK) | - | 350 | - | ps | |

| 공통 모드 트랜지션 면역 | CMTI | VI=VDD 또는 0 VCM=1500V | 35 | 50 | - | kV/µs |

| 데이터 유효성 높은 데이터에 사용 | ten1 | 그림 1 참조 | - | 5.0 | 12 | ns |

| 높음에서 트라이 스테이트까지 비활성화 | ten2 | 그림 1 참조 | - | 65 | 98 | 우리 |

| 입력 드롭 타임에서 유효 출력 드롭 타임까지 | tSD | - | 28 | 45 | ns | |

| 시작 시간(3) | tSU | - | 15 | 45 | µs |

참고: (1) 아이솔레이터 채널의 공칭 출력 임피던스는 약 50Ω±40%이며, 이는 온칩 직렬 저항과 출력 FET 채널 저항의 조합입니다. 부하를 구동할 때 전송 라인 효과가 신호에 영향을 미치는 요인이 될 수 있으므로 출력 핀을 임피던스 제어 PCB 배선에 연결해야 합니다.

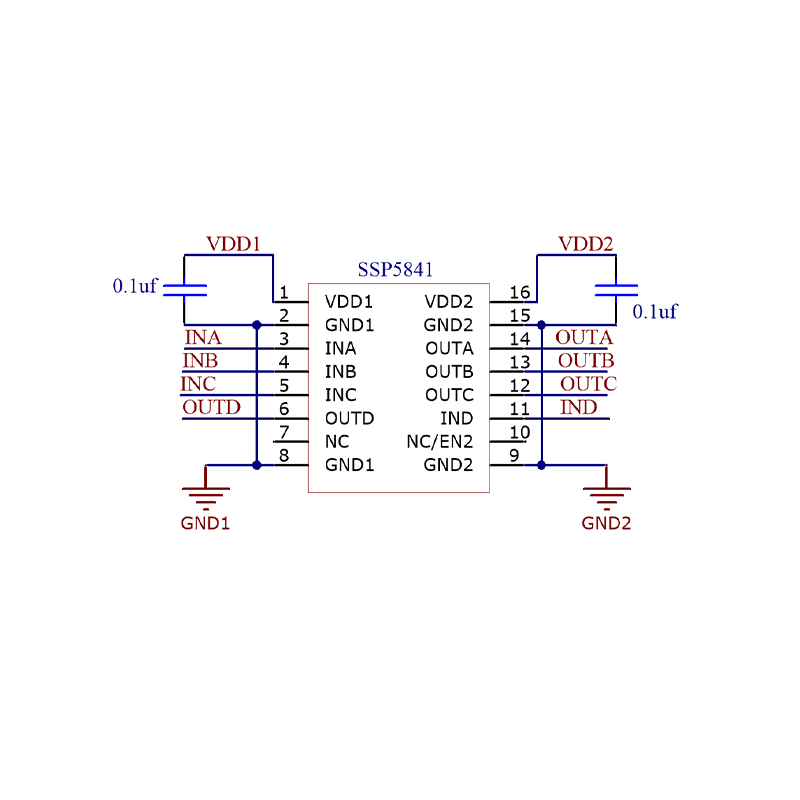

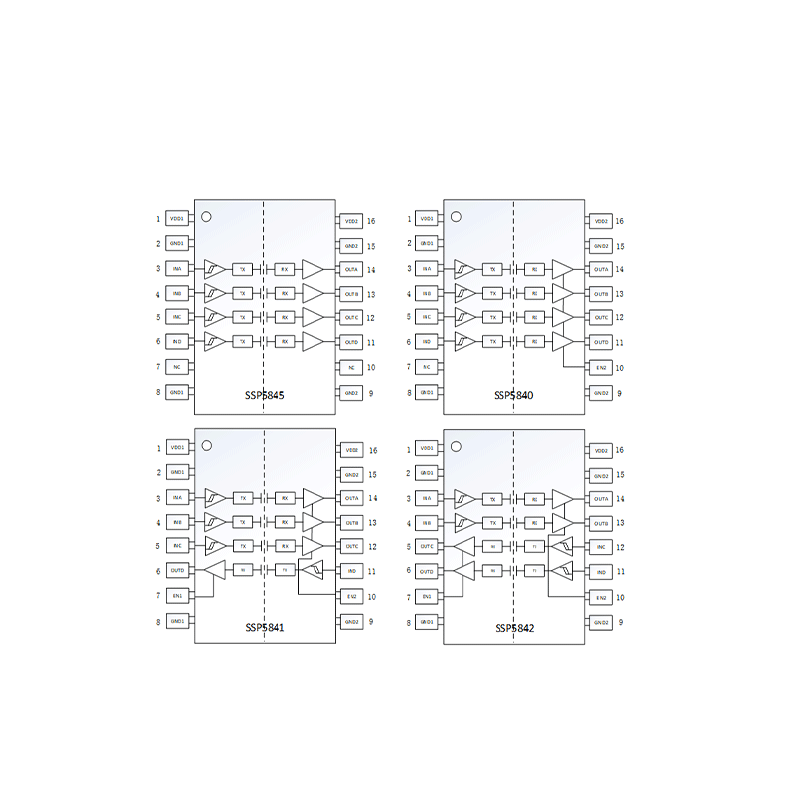

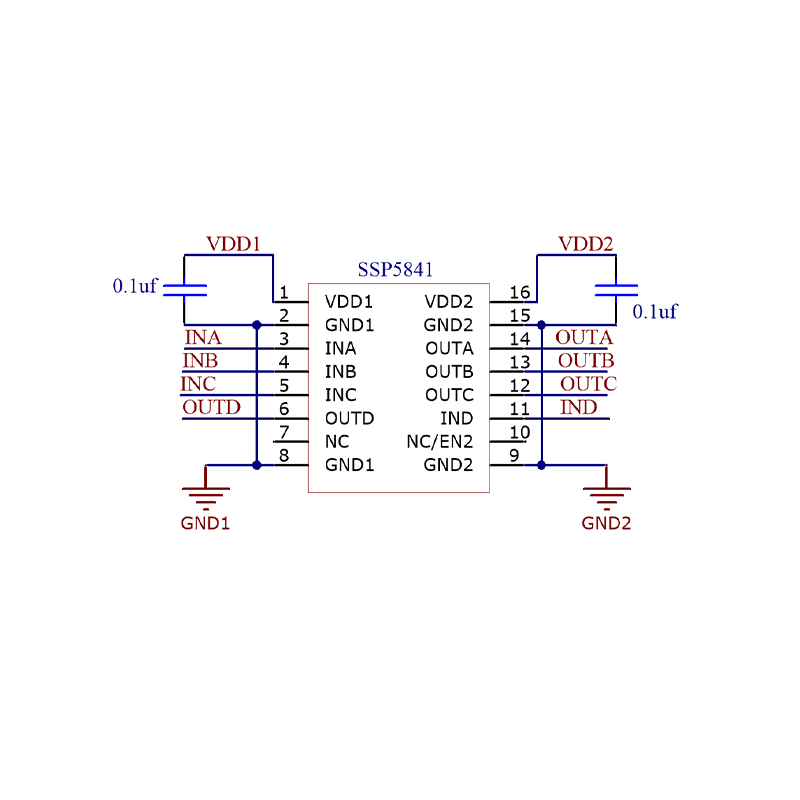

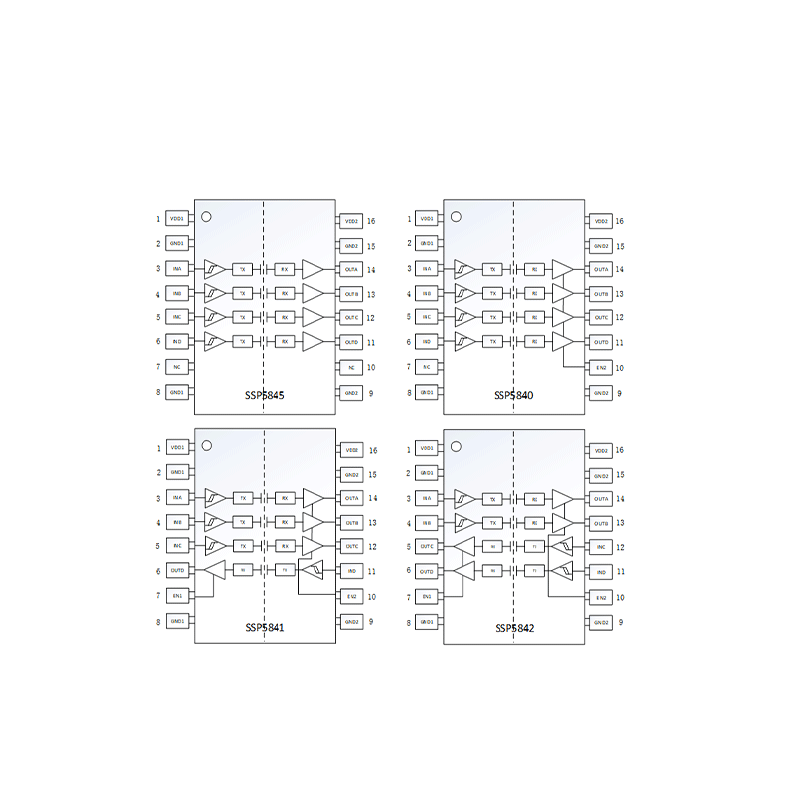

선택 표

| 부품 번호 | 총 채널 수 | 역방향 채널 수 | 기본 출력 레벨 | 패키지 | 포장 방법 | 릴당 장치 수 |

| SSP5840ED | 4 | 0 | 높음 | SOIC-16 | 릴 | 2000 |

| SSP5841ED | 4 | 1 | 높음 | SOIC-16 | 릴 | 2000 |

| SSP5842ED | 4 | 2 | 높음 | SOIC-16 | 릴 | 2000 |

| SSP5845ED | 4 | 0 | 높음 | SOIC-16 | 릴 | 2000 |

| SSP5840BD | 4 | 0 | 낮음 | SOIC-16 | 릴 | 2000 |

| SSP5841BD | 4 | 1 | 낮음 | SOIC-16 | 릴 | 2000 |

| SSP5842BD | 4 | 2 | 낮음 | SOIC-16 | 릴 | 2000 |

| SSP5845BD | 4 | 0 | 낮음 | SOIC-16 | 릴 | 2000 |