特徴

| アプリケーション

|

特徴

| アプリケーション

|

絶対最大定格(1)

特に指定のない限り、Tamb= 25

| パラメータ | シンボル | 価値 | 単位 |

| 電源電圧 | VDD1/VDD2 | -0.5~6 | V |

| A/B入力電圧 | VINA/Vインビー | -0.5~vdd1/vdd2+0.5(2) | V |

| 動作温度 | Tアンブ | -40~125 | ℃ |

| ジャンクション温度 | TJ | 150 | ℃ |

| 保存温度 | Tストッグ | -65~150 | ℃ |

| 端子温度(リフロー) | 260 | ℃ | |

| 定格絶縁 | 5 | KVrms(3) |

注) (1) 上記「絶対最大定格」を超える動作条件では、デバイスに永久的な損傷を与える可能性があります。上記値は、あくまでも動作条件における最大値であり、この仕様範囲外でのデバイスの動作は推奨いたしません。絶対最大定格条件下では、デバイスの安定性に長時間影響を及ぼす可能性があります。

直流電気特性

特に指定のない限り,VDD=2.5V±5% または 3.3V±10% または 5V±10%,Tamb=25℃。

| パラメータ | シンボル | テスト条件 | 最小 | タイプ | マックス | 単位 |

| VDD 低電圧しきい値 | VDDUV+ | VDD1, VDD2 しょうせん | 1.9 | 2.2 | 2.37 | V |

| VDD 低電圧しきい値 | VDD紫外線 | VDD1, VDD2 よこだおし | 1.85 | 2.12 | 2.32 | V |

| VDD 低電圧ヒステリシス | VDDHYS | 50 | 70 | 95 | mV | |

| 正の入力スレッショルド | VT+ | すべての入力が立ち上がる | 1.4 | 1.6 | 1.9 | V |

| 逆入力スレッショルド | VT- | 全入力が故障 | 1.0 | 1.3 | 1.4 | V |

| 入力スレッショルド・ヒステリシス | VHYS | 0.38 | 0.44 | 0.50 | V | |

| ハイレベル入力電圧 | VIH | 2.0 | - | - | V | |

| ローレベル入力電圧 | VIL | - | - | 0.8 | V | |

| ハイレベル出力電圧 | VOH | loh=-4mA | VDD-0.4 | VDD-0.2 | - | V |

| 低レベル出力電圧 | VOL | 笑=4mA | - | 0.2 | 0.4 | V |

| 入力漏れ電流 | IL | - | - | ±10 | μA | |

| 出力インピーダンス(1) | ZO | - | 50 | - | Ω | |

| イネーブル入力電流 | IENH,IENL | VEN=VIH またはVIL | - | 2.0 | - | μA |

| データ・レート | 0 | - | 150 | Mbps | ||

| 最小パルス幅 | - | - | 5.0 | ns | ||

| 伝搬遅延 | tPHL,tPLH | 図2参照 | 5.0 | 9.0 | 15 | ns |

| パルス幅歪み |tPLH-tPHL| | PWD | 図2参照 | - | 0.2 | 4.5 | ns |

| パート間遅延スキュー(2) | tPSK(P-P) | - | 2.0 | 4.5 | ns | |

| チャンネル間 ディレイ・スキュー | t位相偏移変調 | - | 0.4 | 2.5 | ns | |

| ライジング・タイム | ト | CL=15pF、図2参照 | - | 2.2 | 4.0 | ns |

| 落下時間 | ティーエフ | CL=15pF、図2参照 | - | 2.2 | 4.0 | ns |

| ピーク・アイ・ダイアグラム・ジッター | tJIT(PK) | - | 350 | - | ps | |

| コモンモードトランジェント 免疫 | シーエムティーアイ | VI=VDD または 0 VCM=1500V | 35 | 50 | - | kV/µs |

| イネーブル~データ・ハイ・ヴァリッド | tエヌワン | 図1参照 | - | 5.0 | 12 | ns |

| トライステートへのハイ・ディセーブル | tエンツー | 図1参照 | - | 65 | 98 | 私たち |

| 入力降下時間から有効出力降下時間まで | t標準偏差 | - | 28 | 45 | ns | |

| 起動時間(3) | tSU | - | 15 | 45 | μs |

注: (1) アイソレータ・チャンネルの公称出力インピーダンスは約 50Ω±40% であり、これはオンチップ直列抵抗と出力 FET チャンネル抵抗の組み合わせである。負荷を駆動する場合、伝送線路効果が信号に影響を与える要因となるため、出力ピンはインピーダンス制御されたPCB配線に接続する必要があります。

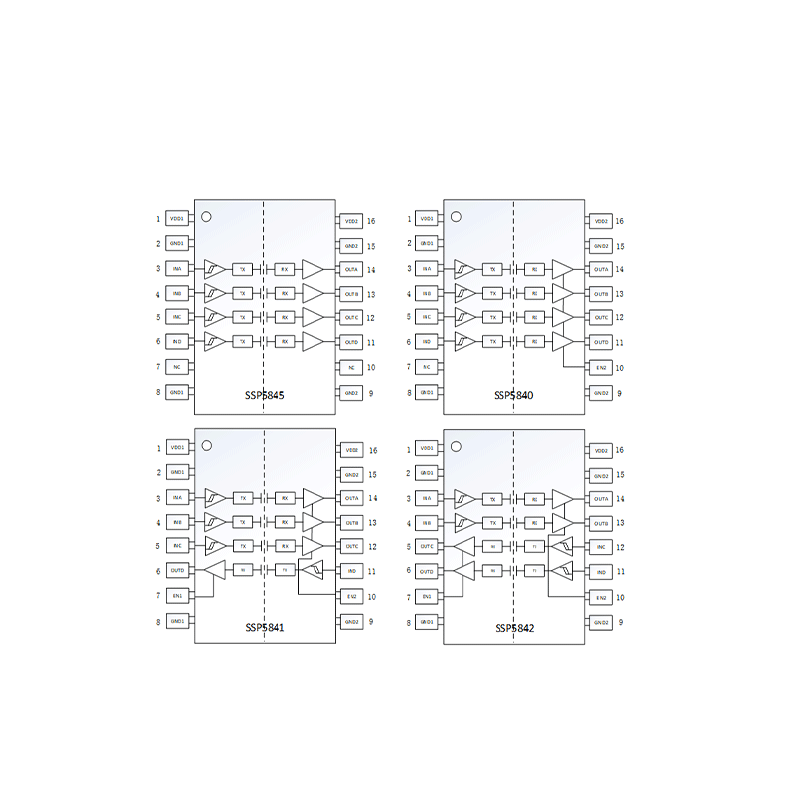

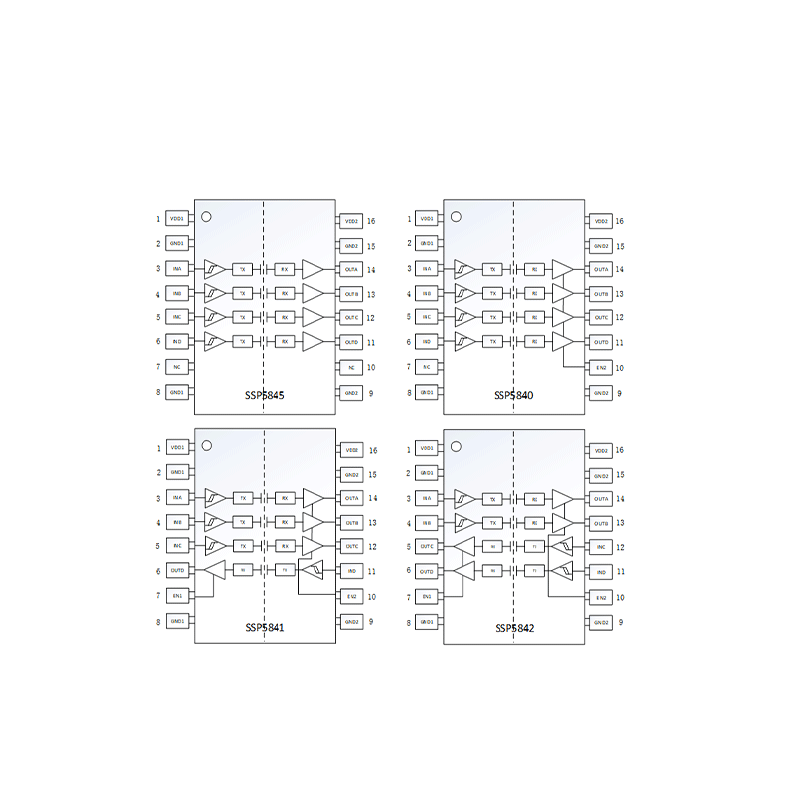

セレクション・テーブル

| 部品番号 | チャンネルの総数 | リバース・チャンネル数 | デフォルト出力レベル | パッケージ | 梱包方法 | リールあたりのデバイス数 |

| SSP5840ED | 4 | 0 | 高い | SOIC-16 | リール | 2000 |

| SSP5841ED | 4 | 1 | 高い | SOIC-16 | リール | 2000 |

| SSP5842ED | 4 | 2 | 高い | SOIC-16 | リール | 2000 |

| SSP5845ED | 4 | 0 | 高い | SOIC-16 | リール | 2000 |

| SSP5840BD | 4 | 0 | 低い | SOIC-16 | リール | 2000 |

| SSP5841BD | 4 | 1 | 低い | SOIC-16 | リール | 2000 |

| SSP5842BD | 4 | 2 | 低い | SOIC-16 | リール | 2000 |

| SSP5845BD | 4 | 0 | 低い | SOIC-16 | リール | 2000 |