Fitur

| Aplikasi

|

Blog

Fitur

| Aplikasi

|

Peringkat Maksimum Absolut(1)

Kecuali ditentukan lain, Tamb= 25 ℃

| Parameter | Simbol | Nilai | Unit |

| Tegangan Suplai | VDD1/VDD2 | -0.5~6 | V |

| Tegangan Input A/B | VINA/VINB | -0,5 ~ VDD1 / VDD2 + 0,5(2) | V |

| Suhu Pengoperasian | Tamb | -40~125 | ℃ |

| Suhu Persimpangan | TJ | 150 | ℃ |

| Suhu Penyimpanan | Tstg | -65~150 | ℃ |

| Suhu Pin (penyolderan reflow) | 260 | ℃ | |

| Isolasi Terukur dengan Tegangan Dudukan | 5 | KVrms(3) |

Catatan: (1) Jika kondisi pengoperasian melebihi "Nilai Maksimum Mutlak" di atas, hal ini dapat menyebabkan kerusakan permanen pada perangkat. Nilai di atas hanyalah nilai maksimum untuk kondisi pengoperasian dan kami tidak menyarankan perangkat beroperasi di luar spesifikasi ini. Stabilitas perangkat dapat terpengaruh dalam kondisi parameter batas absolut untuk waktu yang lama.

Karakteristik Listrik DC

Kecuali ditentukan lain, VDD = 2.5V ± 5% atau 3.3V ± 10% atau 5V ± 10%, Tamb = 25 ℃

| Parameter | Simbol | Kondisi Pengujian | Min | Ketik | Max | Unit |

| Ambang batas tegangan bawah VDD | VDDUV+ | VDD1, VDD2 bangkit | 1.9 | 2.2 | 2.37 | V |

| Ambang batas tegangan bawah VDD | VDDUV- | VDD1, VDD2 gagal turun | 1.85 | 2.12 | 2.32 | V |

| VDD Histeresis tegangan rendah | VDDHYS | 50 | 70 | 95 | mV | |

| Ambang batas masukan positif | VT+ | Semua input naik | 1.4 | 1.6 | 1.9 | V |

| Ambang batas masukan terbalik | VT- | Semua input gagal | 1.0 | 1.3 | 1.4 | V |

| Ambang Batas Masukan Histeresis | VHYS | 0.38 | 0.44 | 0.50 | V | |

| Tegangan Input Tingkat Tinggi | VIH | 2.0 | - | - | V | |

| Tegangan Input Tingkat Rendah | VIL | - | - | 0.8 | V | |

| Tegangan Output Tingkat Tinggi | VOH | loh = -4mA | VDD-0.4 | VDD-0.2 | - | V |

| Tegangan Output Tingkat Rendah | VOL | lol = 4mA | - | 0.2 | 0.4 | V |

| Arus bocor masukan | IL | - | - | ±10 | µA | |

| Impedansi Keluaran(1) | ZO | - | 50 | - | Ω | |

| Mengaktifkan arus input | IENH,IENL | VEN=VIH atau VIL | - | 2.0 | - | µA |

| Kecepatan Data | 0 | - | 150 | Mbps | ||

| Lebar Pulsa Minimum | - | - | 5.0 | ns | ||

| Penundaan Propagasi | tPHL,tPLH | Lihat Gambar 2 | 5.0 | 9.0 | 15 | ns |

| Distorsi Lebar Pulsa |tPLH-tPHL| | PENYANDANG DISABILITAS | Lihat Gambar 2 | - | 0.2 | 4.5 | ns |

| Kemiringan Penundaan Bagian ke Bagian(2) | tPSK (P-P) | - | 2.0 | 4.5 | ns | |

| Saluran-ke-Saluran Tunda Kemiringan | tPSK | - | 0.4 | 2.5 | ns | |

| Waktu naik | tr | CL = 15pF, Lihat Gambar 2 | - | 2.2 | 4.0 | ns |

| Waktu Jatuh | tf | CL = 15pF, Lihat Gambar2 | - | 2.2 | 4.0 | ns |

| Jitter Diagram Mata Puncak | tJIT (PK) | - | 350 | - | ps | |

| Transien Mode Umum Kekebalan | CMTI | VI = VDD atau 0 VCM = 1500V | 35 | 50 | - | kV / µs |

| Aktifkan ke Data tinggi Valid | ten1 | Lihat Gambar 1 | - | 5.0 | 12 | ns |

| Nonaktifkan tinggi ke Tri-State | ten2 | Lihat Gambar 1 | - | 65 | 98 | kami |

| Waktu Penurunan Input ke Waktu Penurunan Output Efektif | tSD | - | 28 | 45 | ns | |

| Waktu Mulai(3) | tSU | - | 15 | 45 | µs |

Catatan: (1) Impedansi keluaran nominal saluran isolator adalah sekitar 50Ω ± 40%, yang merupakan kombinasi dari resistor seri pada chip dan resistor saluran FET keluaran. Saat menggerakkan beban, efek saluran transmisi akan menjadi faktor yang mempengaruhi sinyal, pin output harus dihubungkan ke kabel PCB yang dikontrol impedansi.

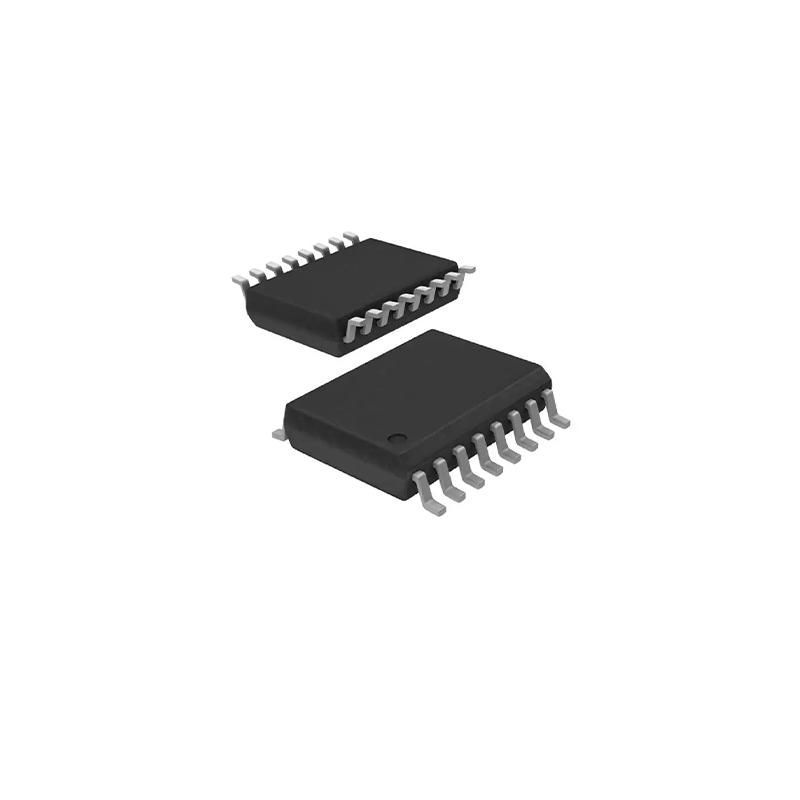

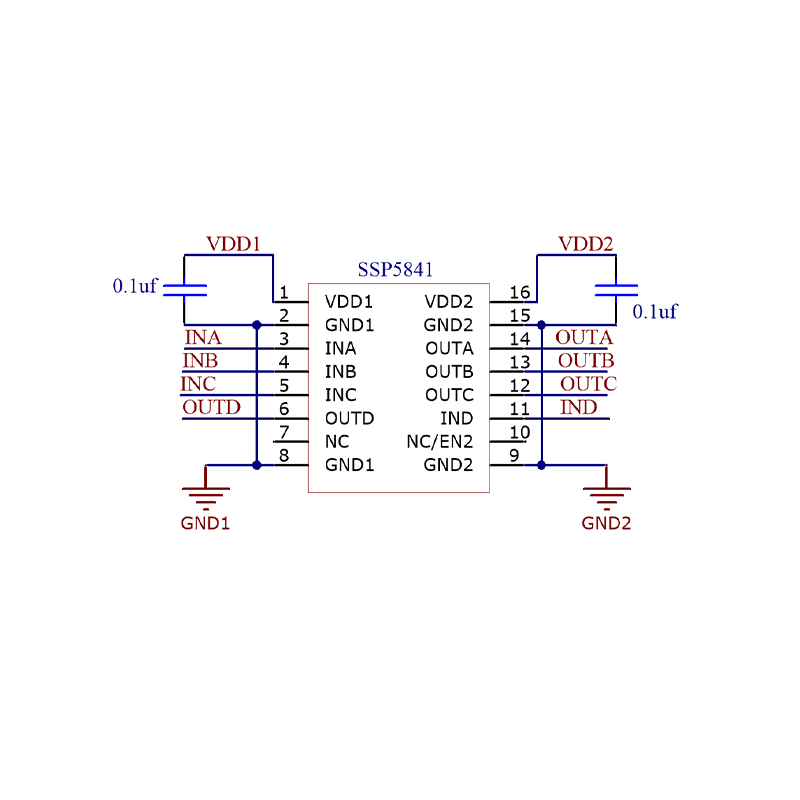

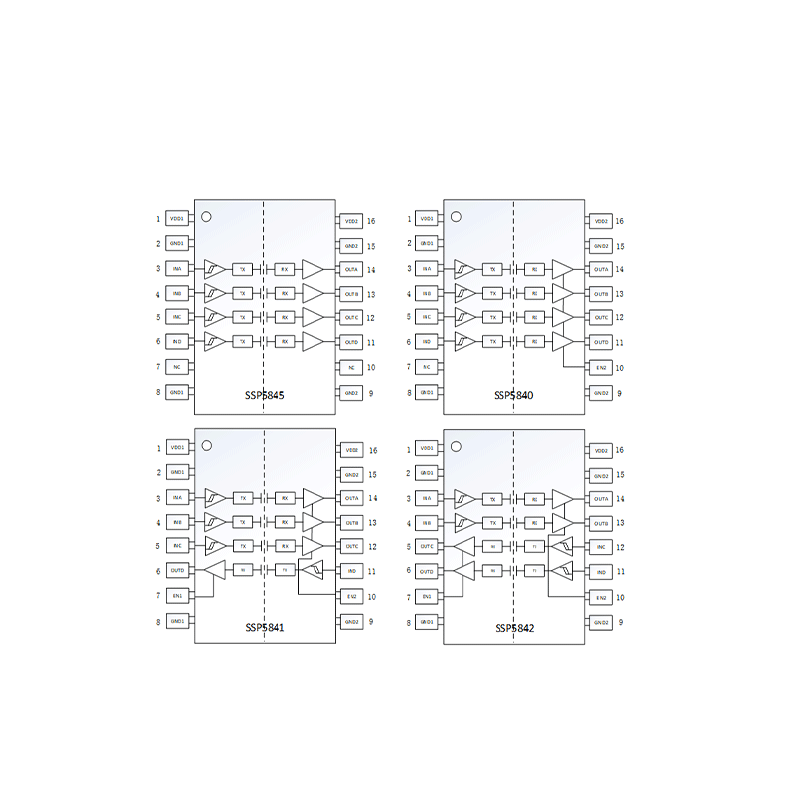

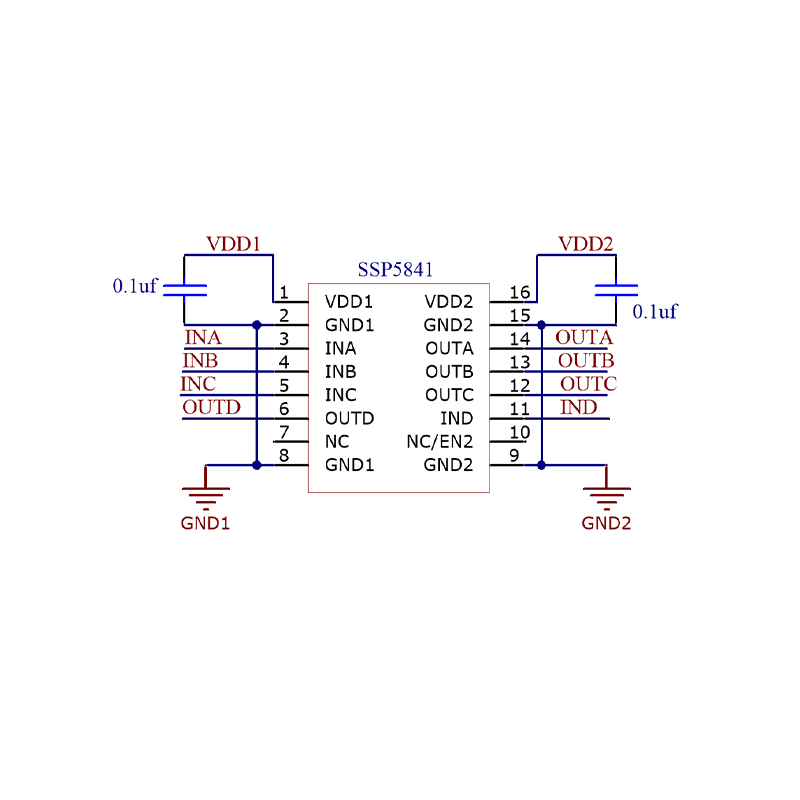

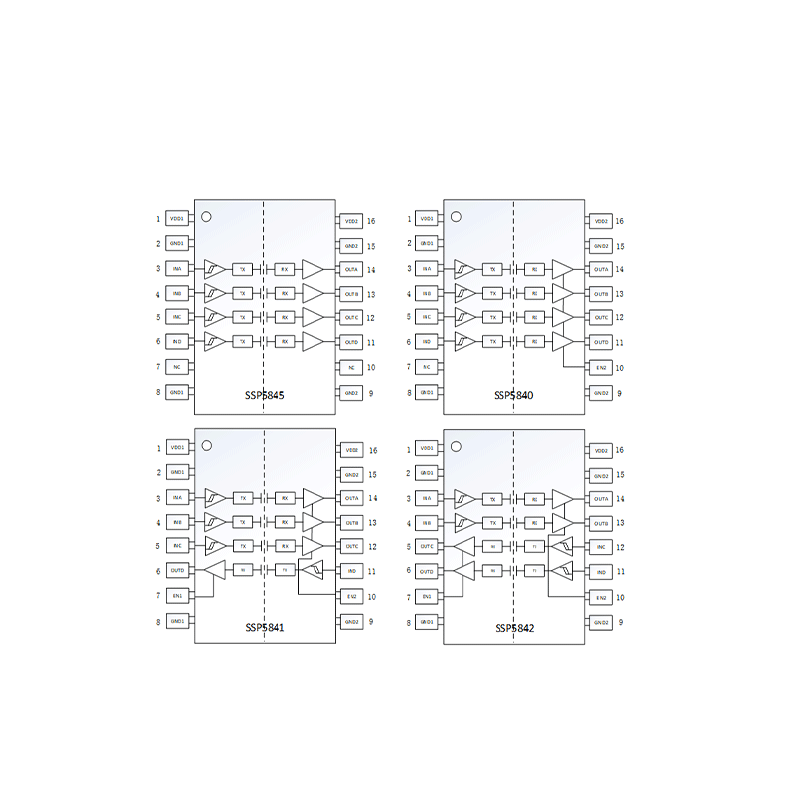

Tabel Pilihan

| Bagian No | Jumlah total saluran | Jumlah saluran balik | Tingkat output default | Paket | Cara Pengemasan | Perangkat per gulungan |

| SSP5840ED | 4 | 0 | Tinggi | SOIC-16 | Reel | 2000 |

| SSP5841ED | 4 | 1 | Tinggi | SOIC-16 | Reel | 2000 |

| SSP5842ED | 4 | 2 | Tinggi | SOIC-16 | Reel | 2000 |

| SSP5845ED | 4 | 0 | Tinggi | SOIC-16 | Reel | 2000 |

| SSP5840BD | 4 | 0 | Rendah | SOIC-16 | Reel | 2000 |

| SSP5841BD | 4 | 1 | Rendah | SOIC-16 | Reel | 2000 |

| SSP5842BD | 4 | 2 | Rendah | SOIC-16 | Reel | 2000 |

| SSP5845BD | 4 | 0 | Rendah | SOIC-16 | Reel | 2000 |

Shanghai Siproin

Perusahaan Mikroelektronika, Ltd.

Selamat datang di kontak Anda.