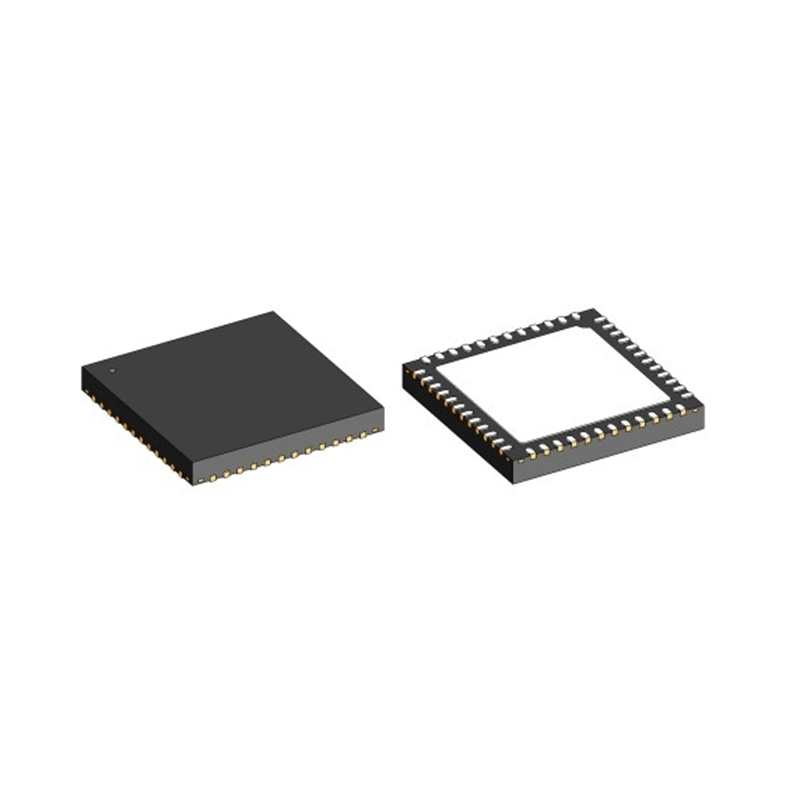

Dieser Chip ist ein hochintegrierter SOC-Chip, der die HPLC-Kommunikation unterstützt. Die physikalische Schicht entspricht dem nationalen Netzstandard Q/GDW12087.41. Er verwendet eine fortschrittliche digital-analoge Hybrid-Designtechnologie und -Prozess, die den analogen HPLC-Front-End-Schaltkreis, den digitalen Signalverarbeitungsschaltkreis, den Speicher und die MCU vollständig auf einem einzigen Chip integriert, wodurch die Datenmodulation und -demodulation sowie die Verarbeitung der Protokollebene abgeschlossen werden.

Der HPLC-Kommunikationskanal dieses Chips verwendet die OFDM-Modulations- und Demodulationsmethode und unterstützt einen Signalfrequenzbereich von 200KHz bis 12MHz. Er kann bis zu 411 Unterträger unterstützen und unterstützt BPSK-, QPSK- und 16QAM-Mapping für verschiedene Ratenmodi, um eine maximale Übertragungsgeschwindigkeit von 12Mbps zu erreichen. Der Chip ist mit einer leistungsstarken Turbo-Vorwärtsfehlerkorrektur- und Interleaving-Technologie ausgestattet. Der Übertragungsmodus ist flexibel und konfigurierbar und ermöglicht eine zuverlässige Kommunikation auch bei starken Rauschstörungen.

Der Chip enthält einen 32-Bit-MCU-Kern und eine Vielzahl von On-Chip-Ressourcen, die den funktionalen Anforderungen der Software und den Anforderungen der Anwendungsentwicklung für die MAC-Schicht und darüber hinaus für die Dual-Mode-Kommunikationsprotokollebene des Stromnetzes entsprechen.