# 2.0MHz, Single Cell DC/DC Converter in 5-Lead SOT-23

#### **FEATURE**

- Uses Tiny Capacitors and Inductor

- Internally Compensated

- Fixed Frequency 2.0MHz Operation

- Operates with V<sub>IN as Low as 1.2V</sub>

- 3V at 30mA from a Single Cell

- 5V at 200mA from 3.3V Input

- 15V at 60mA from Four Alkaline Cells

- High Output Voltage: Up to 34V

- Low Shutdown Current: <1m A

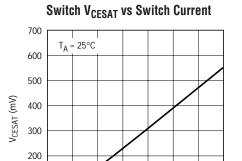

- Low V<sub>CESAT</sub> Switch: 300mV at 300mA

- Tiny 5-Lead SOT-23 Package

### **APPLICATIONS**

- Digital Cameras

- Pagers

- Cordless Phones

- Battery Backup

- LCD Bias

- Medical Diagnostic Equipment

- Local 5V or 12V Supply

- External Modems

- PC Cards

#### **DESCRIPTION**

The SSP8613 is the industry's first 5-lead SOT-23 current mode DC/DC converter. Intended for small, low power applications, it operates from an input voltage as low as 1.2V and switches at 2.0MHz, allowing the use of tiny, low cost capacitors and inductors 2mm or less in height. Its small size and high switching frequency enables the complete DC/DC converter function to take up less than 0.2 square inches of PC board area. Multiple output power supplies can now use a separate regulator for each output voltage, replacing cumbersome quasi-regulated ap-proaches using a single regulator and a custom trans-former.

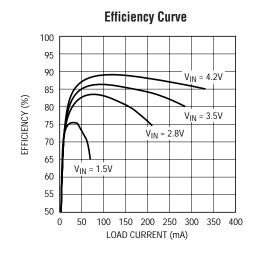

A constant frequency, internally compensated current mode PWM architecture results in low, predictable output noise that is easy to filter. The high voltage switch on the SSP8613 is rated at 36V, making the device ideal for boost converters up to 34V as well as for Single-Ended Primary Inductance Converter (SEPIC) and flyback designs. The device can generate 5V at up to 200mA from a 3.3V supply or 5V at 175mA from four alkaline cells in a SEPIC design.

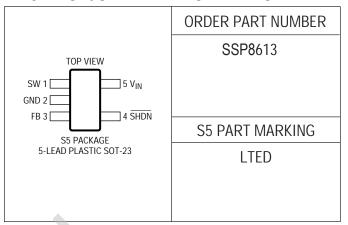

The SSP8613 is available in the 5-lead SOT-23 package.

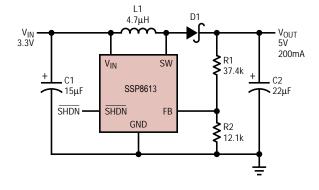

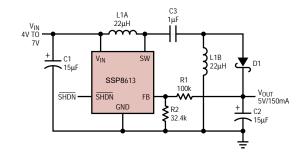

## TYPICAL APPLICATIONS

Figure 1. 3.3V to 5V 200mA DC/DC Converter

## **ABSOLUTE MAXIMUM PATINGS**

| (Note 1)                      |                 |

|-------------------------------|-----------------|

| V <sub>IN</sub> Voltage       | 10V             |

| SW Voltage                    | -0.4V to $36V$  |

| FB Voltage                    | $V_{IN} + 0.3V$ |

| Current into FB Pin           | ±1mA            |

| SHDN Voltage                  | 10V             |

| Maximum Junction Temperature  | 125°C           |

| Operating Temperature Range – | -40° C to 85°   |

|                               |                 |

## PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

## **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operatin temperature range, otherwise specifications are at  $T_A = 25^{\circ}$  C. $V_{IN} = 1.5$ V,  $V_{\overline{SHDN}} = V_{IN}$  unless otherwise noted.

| PARAMETER                     | CONDITIONS                                                                                                     |   | MIN   | TYP          | MAX        | UNITS    |

|-------------------------------|----------------------------------------------------------------------------------------------------------------|---|-------|--------------|------------|----------|

| Minimum Operating Voltage     |                                                                                                                |   |       | 1.2          |            | V        |

| Maximum Operating Voltage     |                                                                                                                |   |       |              | 10         | V        |

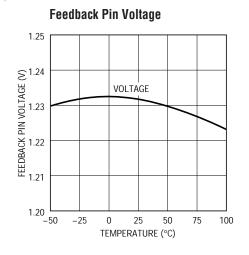

| Feedback Voltage              |                                                                                                                | • | 1.200 | 1.23         | 1.260      | V        |

| FB Pin Bias Current           |                                                                                                                | • |       | 27           | 80         | nA       |

| Quiescent Current             | $V_{\overline{SHDN}} = 1.5V$                                                                                   |   |       | 3            | 4.5        | mA       |

| Quiescent Current in Shutdown | $V_{\overline{SHDN}} = 0V$ , $V_{\overline{IN}} = 2V$<br>$V_{\overline{SHDN}} = 0V$ , $V_{\overline{IN}} = 5V$ |   |       | 0.01<br>0.01 | 0.5<br>1.0 | μA<br>μA |

| Reference Line Regulation     | $1.5V \le V_{IN} \le 10V$                                                                                      |   |       | 0.02         | 0.2        | %/V      |

| Switching Frequency           |                                                                                                                | • |       | 2.0          |            | MHz      |

| Maximum Duty Cycle            |                                                                                                                | • | 82    | 86           |            | %        |

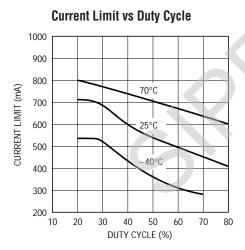

| Switch Current Limit          | (Note 2)                                                                                                       |   | 550   | 800          |            | mA       |

| Switch V <sub>CESAT</sub>     | I <sub>SW</sub> = 300mA                                                                                        |   |       | 300          | 350        | mV       |

| Switch Leakage Current        | V <sub>SW</sub> = 5V                                                                                           |   |       | 0.01         | 1          | μА       |

| SHDN Input Voltage High       |                                                                                                                |   | 1     |              |            | V        |

| SHDN Input Voltage Low        |                                                                                                                |   |       |              | 0.3        | V        |

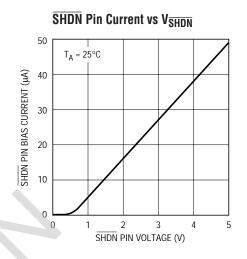

| SHDN Pin Bias Current         | $V_{\overline{SHDN}} = 3V$ $V_{\overline{SHDN}} = 0V$                                                          |   |       | 25<br>0.01   | 50<br>0.1  | μA<br>μA |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: Current limit guaranteed by design and/or correlation to static test.

100

0

# TYPICAL PERFORMANCE CHARACTERISTICS

300 400

SWITCH CURRENT (mA)

700

### **PIN FUNCTIONS**

**SW** (**Pin 1**): Switch Pin. Connect inductor/diode here. Minimize trace area at this pin to keep EMI down.

**GND (Pin 2):** Ground. Tie directly to local ground plane.

**FB** (**Pin 3**): Feedback Pin. Reference voltage is 1.23V. Connect resistive divider tap here. Minimize trace area at FB. Set  $V_{OUT}$  according to  $V_{OUT}$  = 1.23V(1 + R1/R2).

**SHDN (Pin 4):** Shutdown Pin. Tie to 1V or more to enable device. Ground to shut down.

**V<sub>IN</sub> (Pin 5):** Input Supply Pin. Must be locally bypassed.

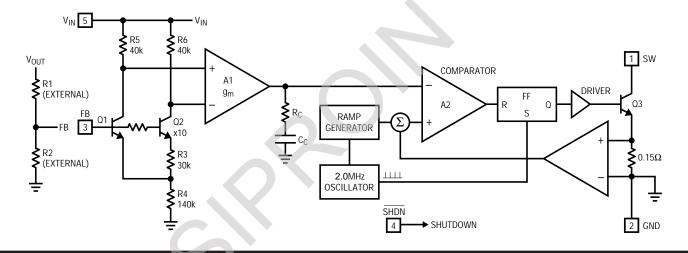

## **BLOCK DIAGRAM**

## **OPERATION**

The SSP8613 is a current mode, internally compensated, fixed frequency step-up switching regulator. Operation can be best understood by referring to the Block Diagram. Q1 and Q2 form a bandgap reference core whose loop is closed around the output of the regulator. The voltage drop across R5 and R6 is low enough such that Q1 and Q2 do not saturate, even when  $V_{IN}$  is 1.2V. When there is no load, FB rises slightly above 1.23V, causing  $V_{C}$  (the error amplifier's output) to decrease. Comparator A2's output stays high, keeping switch Q3 in the off state. As increased output loading causes the FB voltage to decrease, A1's output increases. Switch current is regulated directly on a

cycle-by-cycle basis by the  $V_{\text{C}}$  node. The flip flop is set at the beginning of each switch cycle, turning on the switch. When the summation of a signal representing switch current and a ramp generator (introduced to avoid

subharmonic oscillations at duty factors greater than 50%) exceeds the  $V_{\text{C}}$  signal, comparator A2 changes state, resetting the flip flop and turning off the switch. More power is delivered to the output as switch current is increased. The output voltage, attenuated by external resistor divider R1 and R2, appears at the FB pin, closing the overall loop. Frequency compensation is provided internally by  $R_{\text{C}}$  and  $C_{\text{C}}$ . Transient response can be optimized by the addition of a phase lead capacitor  $C_{\text{PL}}$  in parallel with R1 in applications where large value or low ESR output capacitors are used.

As the load current is decreased, the switch turns on for a shorter period each cycle. If the load current is further decreased, the converter will skip cycles to maintain output voltage regulation.

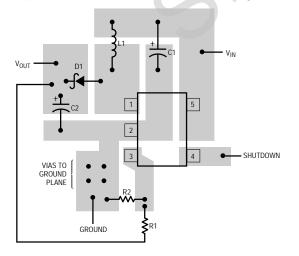

#### **LAYOUT**

The SSP8613 switches current at high speed, mandating careful attention to layout for proper performance. *You will not get advertised performance with careless layouts.* Figure 2 shows recommended component placement for a boost (step-up) converter. Follow this closely in your PCB layout. Note the direct path of the switching loops. Input capacitor C1 *must* be placed close (< 5mm) to the IC package. As little as 10mm of wire or PC trace from C<sub>IN</sub> to V<sub>IN</sub> will cause problems such as inability to regulate or oscillation.

The ground terminal of output capacitor C2 should tie close to Pin 2 of the SSP8613. Doing this reduces dl/dt in the ground copper which keeps high frequency spikes to a minimum. The DC/DC converter ground should tie to the PC board ground plane at one place only, to avoid intro-ducing dl/dt in the ground plane.

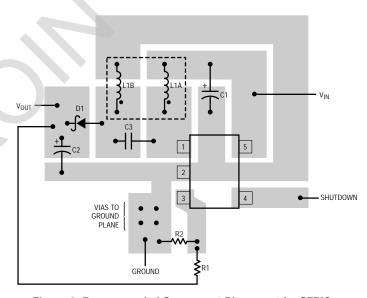

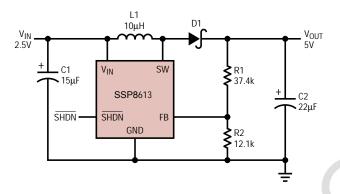

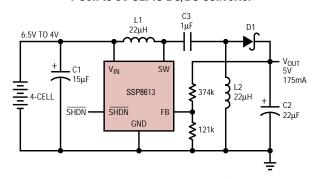

A SEPIC (single-ended primary inductance converter) schematic is shown in Figure 3. This converter topology produces a regulated output voltage that spans (i.e., can be higher or lower than) the output. Recommended component placement for a SEPIC is shown in Figure 4.

Figure 2. Recommended Component Placement for Boost Converter. Note Direct High Current Paths Using Wide PCB Traces. Minimize Area at Pin 3 (FB). Use Vias to Tie Local Ground Into System Ground Plane. Use Vias at Location Shown to Avoid Introducing Switching Currents Into Ground Plane

Figure 3. Single-Ended Primary Inductance Converter (SEPIC) Generates 5V from An Input Voltage Above or Below 5V

Figure 4. Recommended Component Placement for SEPIC

#### COMPONENT SELECTION

#### **Inductors**

Inductor sused with the SSP8613 should have a saturation current rating (where inductance is approximately 70% of zero current inductance) of approximately 0.5A or greater. DCR of the inductors should be 0.5 $\Omega$  or less. For boost converters, inductance should be 4.7 $\mu$ H for input voltage less than 3.3V and 10 $\mu$ H for inputs above 3.3V. When using the device as a SEPIC, either a coupled inductor or two separate inductors can be used. If using separate inductors, 22 $\mu$ H units are recommended for input voltage above 3.3V. Coupled inductors have a beneficial mutual inductance, so a 10 $\mu$ H coupled inductor results in the same ripple current as two 20 $\mu$ H uncoupled units.

Table 1 lists several inductors that will work with the SSP8613, although this is not an exhaustive list. There are many magnetics vendors whose components are suitable for use.

#### **Diodes**

A Schottky diode is recommended for use with the SSP8613. The MBR0520 is a very good choice. Where the input to output voltage differential exceeds 20V, use the MBR0530 (a 30V diode). If cost is more important than efficiency, the 1N4148 can be used, but only at low current loads.

#### **Capacitors**

The input bypass capacitor must be placed physically close to the input pin. ESR is not critical and in most cases an inexpensive tantalum is appropriate.

The choice of output capacitor is far more important. The quality of this capacitor is the greatest determinant of the output voltage ripple. The output capacitor must have enough capacitance to satisfy the load under transient conditions and it must shunt the switched component of current coming through the diode. Output voltage ripple results when this switched current passes through the finite output impedance of the output capacitor. The capacitor should have low impedance at the 1.4MHz switching frequency of the SSP8613. At this frequency, the impedance is usually dominated by the capacitor's equiva-lent series resistance (ESR). Choosing a capacitor with

lower ESR will result in lower output ripple.

Ceramic capacitors can be used with the SSP8613 provided loop stability is considered. A tantalum capacitor has some ESR and this causes an "ESR zero" in the regulator loop. This zero is beneficial to loop stability. The internally compensated SSP8613 does not have an accessible com-pensation node, but other circuit techniques can be em-ployed to counteract the loss of the ESR zero, as detailed in the next section.

Some capacitor types appropriate for use with the SSP8613 are listed in Table 2.

#### **OPERATION WITH CERAMIC CAPACITORS**

Because the SSP8613 is internally compensated, loop sta-bility must be carefully considered when choosing an output capacitor. Small, low cost tantalum capacitors have some ESR, which aids stability. However, ceramic capacitors are becoming more popular, having attractive characteristics such as near-zero ESR, small size and reasonable cost. Simply replacing a tantalum output ca-pacitor with a ceramic unit will decrease the phase margin, in some cases to unacceptable levels. With the addition of

a phase lead capacitor ( $C_{PL}$ ) and isolating resistor (R3), the SSP8613 can be used successfully with ceramic output capacitors as described in the following figures.

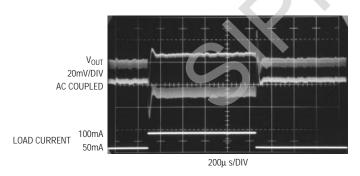

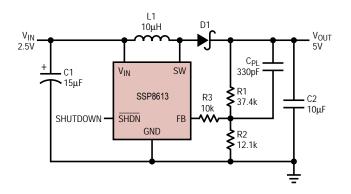

A boost converter, stepping up 2.5V to 5V, is shown in Figure 5. Tantalum capacitors are used for the input and output (the input capacitor is not critical and has little

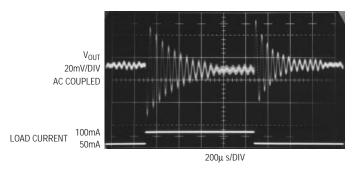

effect on loop stability, as long as minimum capacitance requirements are met). The transient response to a load step of 50mA to 100mA is pictured in Figure 6. Note the "double trace," due to the ESR of C2. The loop is stable and settles in less than 100µs. In Figure 7, C2 is replaced by a 10µF ceramic unit. Phase margin decreases drastically,

Figure 5. 2.5V to 5V Boost Converter with "A" Case Size Tantalum Input and Output Capacitors

Figure 6. 2.5V to 5V Boost Converter Transient Response with 22 $\mu$ F Tantalum Output Capacitor. Apparent Double Trace on V<sub>OUT</sub> Is Due to Switching Frequency Ripple Current Across Capacitor ESR

Figure 7. 2.5V to 5V Boost Converter with  $10\mu F$  Ceramic Output Capacitor, No  $C_{PL}$

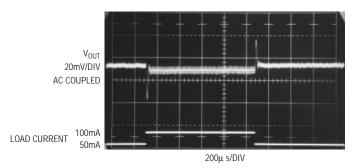

resulting in a severely underdamped response. By adding R3 and  $C_{PL}$  as detailed in Figure 8's schematic, phase margin is restored, and transient response to the same load step is pictured in Figure 9. R3 isolates the device FB pin from fast edges on the  $V_{OUT}$  node due to parasitic PC trace inductance.

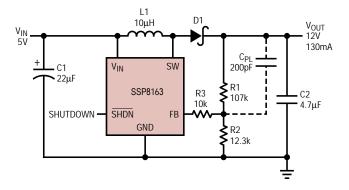

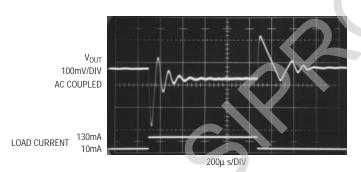

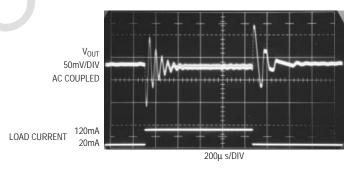

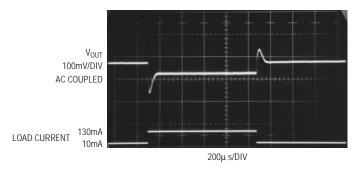

Figure 10's circuit details a 5V to 12V boost converter, delivering up to 130mA. The transient response to a load step of 10mA to 130mA, without  $C_{PL}$ , is pictured in Figure 11. Although the ringing is less than that of the previous example, the response is still underdamped and can be improved. After adding R3 and  $C_{PL}$ , the improved transient response is detailed in Figure 12.

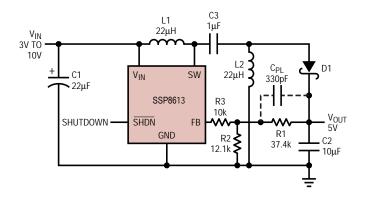

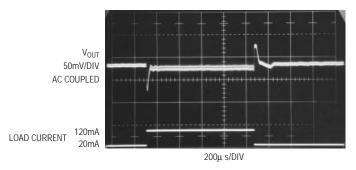

Figure 13 shows a SEPIC design, converting a 3V to 10V input to a 5V output. The transient response to a load step of 20mA to 120mA, without  $C_{PL}$  and R3, is pictured in Figure 14. After adding these two components, the improved response is shown in Figure 15.

Figure 8. 2.5V to 5V Boost Converter with Ceramic Output Capacitor.  $C_{PL}$  Added to Increase Phase Margin, R3 Isolates FB Pin from Fast Edges

Figure 9. 2.5V to 5V Boost Converter with  $10\mu F$  Ceramic Output Capacitor, 330pF  $C_{PL}$  and 10k in Series with FB Pin

Figure 10. 5V to 12V Boost Converter with 4.7 $\mu$ F Ceramic Output Capacitor, C<sub>PL</sub> Added to Increase Phase Margin

Figure 13. 5V Output SEPIC with Ceramic Output Capacitor. C<sub>PL</sub> Adds Phase Margin

Figure 11. 5V to 12V Boost Converter with 4.7µF Ceramic Output Capacitor

Figure 14. 5V Output SEPIC with 10  $\mu F$  Ceramic Output Capacitor. No  $C_{PL},\ V_{IN}$  = 4V

Figure 12. 5V to 12V Boost Converter with 4.7  $\mu\text{F}$  Ceramic Output Capacitor and 200 pF Phase-Lead Capacitor CPL and 10k in Series with FB Pin

Figure 15. 5V Output SEPIC with  $10\mu F$  Ceramic Output Capacitor, 330pF C<sub>PL</sub> and 10k in Series with FB Pin

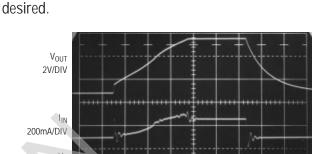

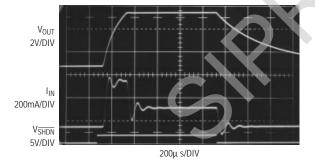

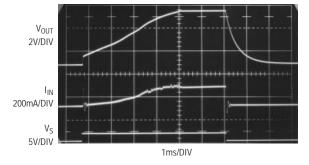

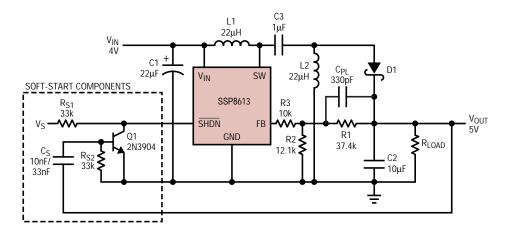

#### START-UP/SOFT-START

When the SSP8613 SHDN pin voltage goes high, the device rapidly increases the switch current until internal current limit is reached. Input current stays at this level until the output capacitor is charged to final output voltage. Switch current can exceed 1A. Figure 16's oscillograph details start-up waveforms of Figure 17's SEPIC into a  $50\Omega$  load without any soft-start. The output voltage reaches final value in approximately  $200\mu$  s, while input current reaches 400mA. Switch current in a SEPIC is 2x the input current, so the switch is conducting approximately 800mA peak.

Soft-start reduces the inrush current by taking more time to reach final output voltage. A soft-start circuit consisting of Q1,  $R_{S1}$ ,  $R_{S2}$  and  $C_{S1}$  as shown in Figure 17 can be used to limit inrush current to a lower value. Figure 18 pictures  $V_{OUT}$  and input current with  $R_{S2}$  of  $33 k\Omega$  and  $C_{S}$  of 10 nF. Input current is limited to a peak value of 200 mA as the

time required to reach final value increases to 1.7ms. In Figure 19,  $C_S$  is increased to 33nF. Input current does not

exceed the steady-state current the device uses to supply

power to the  $50\Omega$  load. Start-up time increases to 4.3ms.

C<sub>S</sub> can be increased further for an even slower ramp, if

Figure 18. Soft-Start Components in Figure 17's SEPIC Reduces Inrush Current.  $C_{SS}$  = 10nF,  $R_{LOAD}$  = 50 $\Omega$

500μ s/DIV

5V/DIV

Figure 16. Start-Up Waveforms of Figure 17's SEPIC Into  $50\Omega$  Load

Figure 19. Increasing C<sub>S</sub> to 33nF Further Reduces Inrush Current.  $R_{LOAD} = 50\Omega$

Figure 17. 5V SEPIC with Soft-Start Components

## TYPICAL APPLICATIONS

#### 4-Cell to 5V SEPIC DC/DC Converter

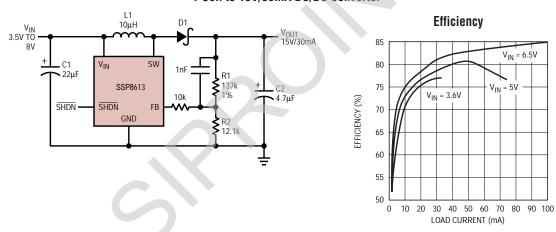

#### 4-Cell to 15V/30mA DC/DC Converter

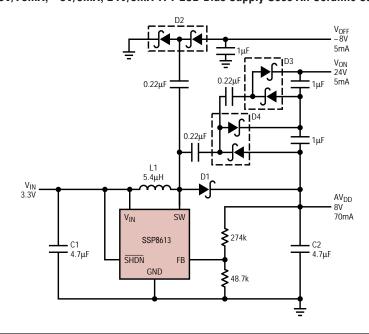

3.3V to 8V/70mA, -8V/5mA, 24V/5mA TFT LCD Bias Supply Uses All Ceramic Capacitors

## **TYPICAL APPLICATIONS**

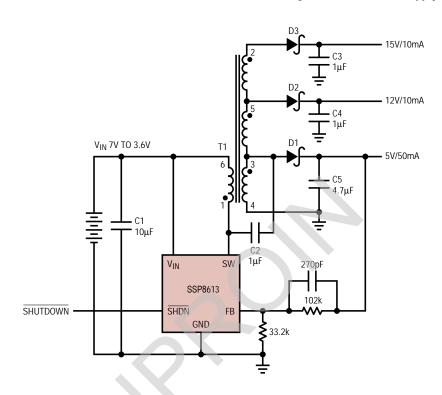

4-Cell to 5V/50mA, 12V/10mA, 15V/10mA Digital Camera Power Supply

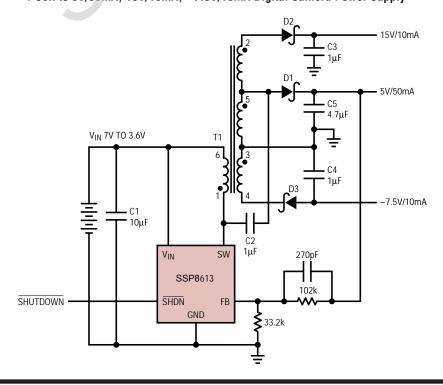

4-Cell to 5V/50mA, 15V/10mA, -7.5V/10mA Digital Camera Power Supply

## TYPICAL APPLICATIONS

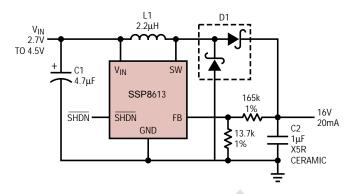

#### Li-Ion to 16V/20mA Step-Up DC/DC Converter

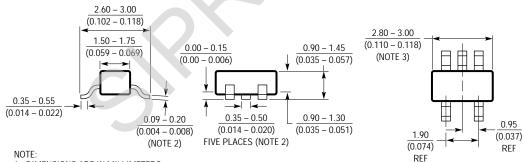

# PACKAGE DESCRLPTION Dimensions in inches (millimeters) unless otherwise noted.

#### S5 Package 5-Lead Plastic SOT-23

- 1. DIMENSIONS ARE IN MILLIMETERS

- 2. DIMENSIONS ARE INCLUSIVE OF PLATING

- 3. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

- 4. MOLD FLASH SHALL NOT EXCEED 0.254mm

- 5. PACKAGE EIAJ REFERENCE IS SC-74A (EIAJ)