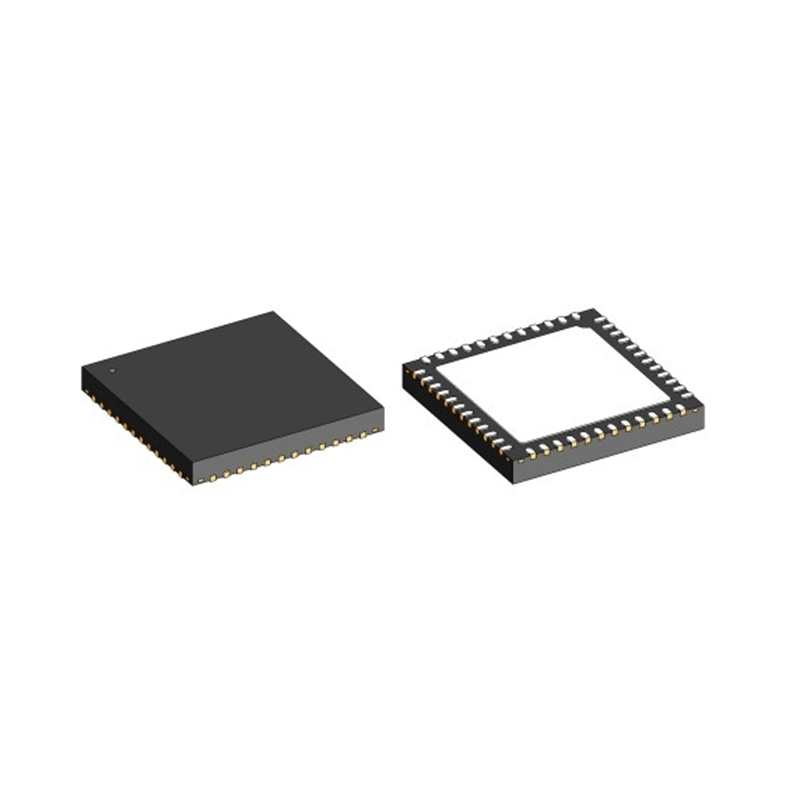

PU32F407

This chip is a highly integrated SOC chip that supports HPLC communication. The physical layer complies with the national grid standard Q/GDW12087.41. It adopts advanced digital-analog hybrid design technology and process, fully integrating the HPLC analog front-end circuit, digital signal processing circuit, memory, and MCU onto a single chip, thereby completing data modulation and demodulation as well as protocol layer processing.

The HPLC communication channel of this chip uses OFDM modulation and demodulation method, supporting a signal frequency range of 200KHz to 12MHz. It can support up to 411 subcarriers and supports BPSK, QPSK and 16QAM mapping for different rate modes to achieve a maximum transmission speed of 12Mbps. The chip is equipped with a powerful Turbo forward error correction and interleaving technology, and the transmission mode is flexible and configurable, enabling reliable communication even under strong noise interference.

This chip integrates a 32-bit MCU core and a rich set of on-chip resources, which can meet the software functional requirements and application development needs of the MAC layer and above of the power grid dual-mode communication protocol layer.

_画板-1@2x.png)