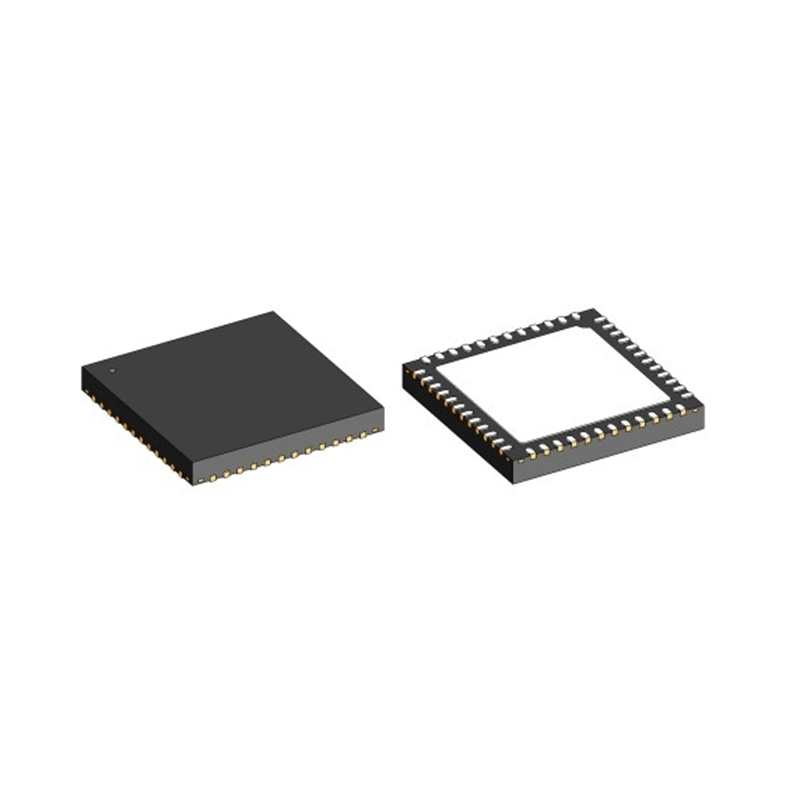

PU32F407

Este chip es un chip SOC altamente integrado que admite la comunicación HPLC. La capa física cumple la norma de red nacional Q/GDW12087.41. Adopta tecnología y procesos avanzados de diseño híbrido digital-analógico, integrando plenamente el circuito frontal analógico HPLC, el circuito de procesamiento de señales digitales, la memoria y la MCU en un único chip, completando así la modulación y demodulación de datos, así como el procesamiento de la capa de protocolo.

El canal de comunicación HPLC de este chip utiliza el método de modulación y demodulación OFDM, que admite una gama de frecuencias de señal de 200KHz a 12MHz. Puede soportar hasta 411 subportadoras y admite el mapeo BPSK, QPSK y 16QAM para diferentes modos de tasa con el fin de alcanzar una velocidad de transmisión máxima de 12Mbps. El chip está equipado con una potente tecnología Turbo de intercalación y corrección de errores hacia delante, y el modo de transmisión es flexible y configurable, lo que permite una comunicación fiable incluso bajo fuertes interferencias de ruido.

Este chip integra un núcleo MCU de 32 bits y un rico conjunto de recursos en chip, que pueden satisfacer los requisitos funcionales de software y las necesidades de desarrollo de aplicaciones de la capa MAC y superiores de la capa de protocolo de comunicación de modo dual de la red eléctrica.

_画板-1@2x.png)